ALC4030-CG

- 品牌:

REALTEK/瑞昱

- 封装:

QFN-48

- 数量:

4600

- 备注:

ALC4030-CG 功能描述:IC BUFF 8BIT NON-INV DL 56TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:16000 标准包装:1,000 系列:74ABT 逻辑类型:寄存收发器,非反相 元件数:1 每个元件的位元数:8 输出电流高,低:32mA,64mA 电源电压:4.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295,7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR)

- 批号:

21+

- 价格:

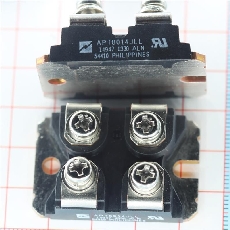

AR8035-AL1A

- 品牌:

QUALCOMM/高通

- 封装:

QFN40

- 数量:

2580

- 备注:

Symbol Pin Type Deion MDI TRXP0, TRXN0 9, 10 IA, OA Media-dependent interface 0, 100 transmission line TRXP1, TRXN1 12, 13 IA, OA Media-dependent interface 1, 100 transmission line TRXP2, TRXN2 15, 16 IA, OA Media-dependent interface 2, 100 transmission line TRXP3, TRXN3 18, 19 IA, OA Media-dependent interface 3, 100 transmission line RGMII GTX_CLK 33 I, PD RGMII transmit clock, 125 MHz digital. Adding a 22 damping resistor is recommended for EMI design near MAC side. RX_CLK 31 I/O, PD 125MHz digital, adding a 22 damping resistor is recommended for EMI design near PHY side. RX_DV 30 I/O, PD RGMII receive data valid RXD0 29 I/O, PD RGMII received data 0 RXD1 28 I/O, PD RGMII received data 1 RXD2 26 I/O, PD RGMII received data 2 RXD3 25 I/O, PD RGMII received data 3 TX_EN 32 I, PD RGMII transmit enable TXD0 34 I, PD RGMII transmit data 0 TXD1 35 I, PD RGMII transmit data 1 TXD2 36 I, PD RGMII transmit data 2 TXD3 37 I, PD RGMII transmit data 3 Management InterfaceInterrupt MDC 40 I, PU Management data clock reference MDIO 39 I/O, D, PU Management data, 1.5K pull-up to 3.3V/2.5V INT 20 I/O, D, PD Interrupt Signal to System; default OD-gate, needs an external 10K pull-up, active low; can be configured to I/O by register, active high. LED LED_ACT 21 I/O, PU Parallel LED output for 10/100/1000 BASE-T activity, active blinking. LED active based upon power-on strapping. If pulled up — active low, if pulled down — active high LED_1000 22 I/O, PU Parallel LED output for 1000 BASE-T link, LED active based upon power-on strapping. If pulled up — active low, if pulled down — active high

- 批号:

21

- 价格: